Contract No: 12783-001-05 49 **Provide Medium to Long-term Computer**

Science Research Relevant to the Goals of the Advanced Simulation and Computing

(ASC) Program

LACSI Task

Los Alamos Computer Science Institute

**External Computer Science Research**

# FY06 Statement of Work

September 26, 2005

# **Application and System Performance**

Develop compiler and run-time technology that will help application developers achieve a high fraction of peak performance on large-scale parallel computing systems.

The specific tasks and deliverables are described in Appendix A, Section 1.

# **Components**

This effort will incrementally develop two long-term goals.

- 1) Develop *component architectures for high performance computing* that will make it easy to rapidly and conveniently integrate components into complete applications. These frameworks should produce efficient applications from scripts in high-level or standard languages and preprocessed component libraries within reasonable compile times.

- 2) Develop practical systems for *automatic tuning and retargeting of high-performance components* and *libraries* using computation-intensive tuning runs on sample inputs.

Specific tasks and deliverables are described in Appendix A, Section 2.

#### **Systems**

The systems activity addresses research and advanced development of computer subsystems, both hardware and software, of strategic interest to present and future ASC architectures.

The systems activity focuses on efficient and fault-tolerant implementations of networking protocols and message passing libraries for high-end parallel systems.

The specific tasks and deliverables are described in Appendix A, Section 3.

### **Computational Science**

The computational science activity focuses on research and development in two areas:

- Develop advanced numerical methods for diffusion equations in heterogeneous media on distorted polyhedral meshes.

- Develop code-based sensitivity methods for verification and validation of scientific codes.

The specific tasks and deliverables are described in Appendix A, Section 4.

# **LACSI Management & Community Interaction**

The implementation strategy and tasks associated with managing the academic LACSI projects are detailed in Appendix A, Section 5.1.

LACSI will foster collaborative relationships between LACSI participants at LANL and at the LACSI academic sites. Activities will include:

- Support scientific collaboration visits to Los Alamos National Lab to integrate research products into operations.

- In conjunction with LANL, organize, host, and otherwise support a series of technical workshops on topics related to the LACSI technical vision.

- Host an annual symposium to showcase LACSI results and to provide a forum for presenting outstanding research results from the national community in areas overlapping the LACSI technical vision.

Specific tasks and deliverables are described in Appendix A, Section 5.3.

#### **Deliverables**

Reports and briefings and briefings on milestones/deliverables will be provided as required.

# Appendix A

# **Los Alamos Computer Science Institute**

#### FY 2006 Statement of Work

The Los Alamos Computer Science Institute (LACSI) was created to foster internationally recognized computer science and computational science research efforts relevant to the goals of Los Alamos National Laboratory (LANL). LACSI is a collaborative effort between LANL and the Rice University Center for Research on High Performance Software (HiPerSoft), along with its partner institutions: The University of Houston (UH), the University of New Mexico (UNM), the University of North Carolina at Chapel Hill (UNC), and the University of Tennessee at Knoxville (UTK).

LACSI's principal goal is to conduct basic research in computer and computational science that has relevance to LANL's mission. The funding is not intended to support advanced development efforts, although some such efforts may be spun out to produce software and tools that will be directly useful to end users. Secondary goals of the Institute are to increase the national and international stature of LANL computer science and to engage the high-performance computing research community in problems of importance to LANL.

For FY06, LACSI activities will cover a broad spectrum of areas of research, including strategies for measuring, analyzing, and improving application and system performance; components and component integration systems; computer systems and networking; and computational science. These research areas are covered in four subsequent sections of the statement of work. Every section includes two subsections, each describing a coherent, coordinated research activity, a set of tasks to be carried out, and a discussion of the relevance of the proposed work to the Weapons Program.

Following the four research sections, there is an additional section that covers management and community interaction. The management section includes a detailed discussion of the new management and planning cycle for LACSI. Community interactions include the enormously successful LACSI Annual Symposium and several other outreach programs carried out by the Institute.

Taken together, the proposed LACSI activities represent a broad and deep collection of projects that can have an enormous positive impact on high performance computing and communications within the DOE Weapons Program.

# 1. Application and System Performance

#### 1.1 Integrated Performance and Reliability of Extreme-scale Systems

#### Supported Personnel:

**Project Leads:** John Mellor-Crummey, Rice, <u>johnmc@cs.rice.edu</u>; Jack Dongarra, UTK, <u>dongarra@cs.utk.edu</u>; Daniel Reed, UNC, <u>Dan\_Reed@unc.edu</u>, Patrick Bridges, UNM, <u>bridges@cs.unm.edu</u>

Other Supported Personnel: Rice: Rob Fowler

LANL Point of Contact: Adolfy Hoisie, hoisie@lanl.gov

#### 1.1.1 Vision and Motivation

Building scientific applications that can exploit extreme-scale parallel systems effectively is difficult. The goal of research on performance and reliability of large-scale systems is to develop tools and technologies that help application scientists harness the power of extreme-scale parallel systems for solving computation-intensive problems.

The level of parallelism in extreme-scale systems and the need to exploit parallelism on multiple levels poses a formidable challenge to achieving scalable performance. Furthermore, the architectural complexity of extreme-scale systems makes it hard to write programs that can fully exploit their capabilities. Today's extreme-scale systems include complex processors, deep memory hierarchies and complex heterogeneous interconnects. A broad spectrum of issues affects application performance, including operating system activity, load imbalance, serialization, underutilization of processor functional units, data copying, poor temporal and spatial locality of data accesses, exposed communication latency, high communication frequency, large communication bandwidth requirements, and ineffective network utilization. To achieve a significant fraction of a system's potential performance requires careful scheduling of an application's operations, data accesses, and communication.

On extreme-scale systems, performance and reliability are inseparable. The large number of components in extreme-scale parallel systems makes component failure inevitable; therefore, long-running computation-intensive applications must be resilient to transient and permanent hardware faults or risk being unable to run to completion. The most popular parallel programming paradigm, MPI, has little support for reliability. When a node fails, all MPI processes are killed and the user loses all computation performed since the last application-initiated checkpoint.

Many challenging problems must be solved to understand how to implement scientific applications so that they can achieve scalable high performance and are resilient to failure on extreme-scale parallel systems. We propose a program of research that aims to develop technologies that support measuring, analyzing, modeling, and improving the performance and reliability of applications on current and future generations of extreme-scale parallel architectures. The principal aims of this research effort are to

- understand application and system performance and failure modes on present-day extreme-scale

architectures through the development and application of technologies for measurement and

analysis of program and system behavior,

- model the behavior of applications to understand factors affecting their performance and reliability on current and future generations of computer systems,

- devise software strategies to ameliorate application performance bottlenecks and failure susceptibility on today's architectures, and

• explore technologies to support fault tolerance, including capabilities for monitoring the health of system components, predicting impending faults, and proactively avoiding faults.

This work will address aspects of performance and reliability spanning both applications and underlying hardware.

#### 1.1.2 Research Plan

To address the problem of developing applications for extreme-scale systems that deliver high performance and are resilient to failure, we propose research in the areas of measuring performance and component health, analyzing performance and reliability, modeling application and system performance and reliability, exploring techniques for constructing failure-resilient programs, and evaluating alternative architectures that can yield increased performance and greater reliability.

#### **Measuring Performance and Reliability**

Extreme-scale systems require monitoring for a variety of purposes. Performance monitoring is needed to evaluate program behavior and resource utilization to understand why and where applications are inefficient. Health monitoring of status information such as temperature and power consumption is necessary on extreme-scale systems to anticipate or detect failures, which are inevitable on such systems because of their scale.

For measurement tools to be useful for monitoring production programs on extreme-scale systems, they must

- have low overhead that does not distort application performance or system behavior,

- work with multi-lingual, parallel, optimized code without modification,

- analyze not only user programs but their interplay with binary-only libraries, the operating system kernel and system processes,

- support programs with large-scale, possibly heterogeneous parallelism,

- record data of only modest size, and

- scale to tens of thousands of nodes.

In general, performance problems on extreme-scale systems are varied and complex. To understand the performance of parallel applications, one must capture detailed information about their behavior, including the interplay of computation, consumption of and contention for resources (e.g., network and I/O), communication, synchronization, and serialization. The key research challenge is to devise effective strategies for integrated measurement of such aspects of program behavior. These measurements must be sufficient to provide insights into the interplay between these different aspects of program behavior and yet introduce only low monitoring overhead so they can be used on production runs. For performance measurements to be most useful to application developers, it must be possible to correlate them with the application's source code.

The appropriate strategy for collecting performance measurements depends upon the aspect of program behavior under study and the intended uses of the performance data. Performance data for an application may be collected for off-line analysis or it may be collected to enable an application to evaluate its own efficiency and adapt its behavior in response to its findings. Key strategies for gathering performance data include statistical sampling of events (sampling may be either system wide or within individual application processes), using instrumented communication libraries, and inserting instrumentation into programs via source code transformations, or by rewriting application and library binaries at link time, program launch, or during execution.

#### Measuring and Attributing Node Performance

For modern modular programs, knowing the context in which costs were incurred is vital to understanding how to address performance problems. For instance, rather than knowing that a program spends time in a particular solver, it is much more informative to know that when the solver is called with preconditioned matrices, it is fast; otherwise, it is much slower. Similarly, for parallel programs that invoke communication operations in many places, knowing that the program spends a lot of time waiting for communication is not particularly helpful for pinpointing the problem. In contrast, knowing that most waiting time is associated with a particular communication event is the first step to determining whether load imbalance, serialization or communication frequency is to blame.

To attribute costs precisely to execution contexts within programs, we propose to design, build, evaluate, and disseminate open-source compiler and runtime mechanisms for efficiently collecting calling context for both synchronous and asynchronous events. Synchronous events include memory allocation and communication. Asynchronous events include hardware performance counter overflows and timer expiration. We need to collect information about both classes of events during the execution of *optimized* code. Rather than instrumenting each function to log its entry and exit so that calling context information is always available (as gprof does), we collect calling context on demand by stack unwinding. Collecting calling context efficiently for optimized code is tricky. In particular, for asynchronous events, monitoring code must be able to unwind the call stack from *any* point in the program execution, even procedure prologues or epilogues. For this case, compiler support or binary analysis is needed to determine exactly where in the machine state the return address of the caller resides. This work will build on prior work at Rice on AlphaServer platforms, which lacked sufficient compiler support to fully realize this vision, and ongoing work on Opteron platforms for which we are prototyping necessary compiler support in the gcc compiler infrastructure.

To date, our research on measuring application node performance has focused on static parallelism of threads and processes. Programming models and architectures under development as part of DARPA's HPCS project heavily rely on dynamic parallelism. We propose to explore strategies for understanding system performance for applications and systems making use of dynamic parallelism.

#### Measuring Performance Beyond Processors

The PAPI library has standardized access to hardware event counters available on most modern microprocessors by providing standard routines and a standard set of performance metrics. Counters on processors measure events such as cycle and operation counts, functional unit status, cache and memory accesses, and branch behavior. Other components besides the processor, such as memory chips, network interface cards, and network switches, also have counters that monitor various events related to system performance and reliability. Unlike on-processor counters, off-processor counters usually measure events system wide rather than for a process or thread-specific context. However, when an application has exclusive use of a machine partition, it may be possible to interpret such counts in the context of the application. It may also be possible to correlate process-specific events counts with system-wide counts using a "data mining" approach based on multivariate statistical analysis.

The current situation with off-processor counters is similar to the situation that existed with on-processor counters before PAPI. There are many platform-specific interfaces, some of which are undocumented. We propose to develop standard routines for accessing off-processor counters on a range of platforms and networks. We have begun working on an interface to counters available on Myricom network switches. The Infiniband standard also has definitions of measurement hooks. The Cray X1 has E-chip and M-chip counters. The challenge will be to try to develop as portable an interface as possible while still providing access to information that is necessarily somewhat platform-specific. In addition to routines to control and access counters, we plan to provide query routines that will provide information about what counters and events are available, including both standardized and platform-specific events.

#### Measuring Communication

To understand the performance of parallel applications on extreme-scale systems, one must understand the end-to-end costs of communication and delays that result from load imbalance or serialization. For this purpose, we have begun to explore a message-centric monitoring approach that involves gathering and propagating information as messages traverse the system. Using this approach, each message is augmented with a monitoring summary that compactly encodes information related to the message, e.g., how much time was spent generating the data contained in the message. Message-centric monitoring trades the centralized global view of trace-based systems for a decentralized, weakly consistent view of system behavior to approach the low overheads and online availability provided by statistical monitoring techniques. Making this monitoring approach efficient will require developing low-overhead representations of performance and reliability data, and controlling monitoring overhead by a combination of sampling and adaptive monitoring.

Thus far, we have separately explored two strategies for message-centric monitoring: vertical monitoring of message costs on a single node, and horizontal monitoring that combines monitoring summaries from multiple incoming messages, creates a new monitoring summary from this data, and attaches it to outgoing messages. Our current prototypes show that we can gather vertical monitoring information on Linux cluster nodes using a modified version of the Linux Trace Toolkit with 3% overhead for the NAS parallel benchmarks, and that we can efficiently propagate horizontal monitoring information about LA-MPI runtime performance with similar overheads. We now need to integrate these prototypes, developed at UNM, into a single system for monitoring all operating system and message passing costs for a large-scale parallel scientific application, integrate them will the application-level monitoring tools developed at Rice, and evaluate their accuracy and overhead on large-scale machines with the ASCI Purple benchmarks.

We propose to explore a sample-based approach to message-centric monitoring to enable tunable control of measurement accuracy and instrumentation overhead. This would enable message-centric monitoring to be used on production applications and system software. If message-centric monitoring is available for production applications, it can be used to audit them to verify that their behavior matches the characteristics of previously gathered performance profiles. Such audits could be used to detect performance anomalies caused by new data sets or system software changes. In addition, online availability of message-centric monitoring could also be used to optimize application load-balancing decisions and to drive MPI protocol adaptations to improve application performance.

#### Measuring Node and System Health and Reliability

Component failure is inevitable on extreme-scale systems. Long-running jobs must expect to encounter faults and take appropriate action to enable systems and applications to continue operating even when some components fail. Without the ability to anticipate or notice and tolerate component failure, the mean time to failure (MTBF) of systems with tens of thousands of commodity components, even when operated as quasi-independent partitions, will continue to decline and will severely limit the ability to solve complex problems. To anticipate component failures, we propose to develop an extended health monitoring infrastructure and support for assessing the thermal environment of extreme-scale systems.

During the past year, Reed's team at UNC has developed a health monitoring system library and a Health Application Programming Interface (HAPI) for discovery and use of health-related diagnostic information on Linux clusters. HAPI acquires fault indicator data via (a) vendor provided Self-Monitoring Analysis and Reporting Technology (SMART) for disk warnings such as seek and read/write retries; (b) Advanced Configuration and Power Interface (ACPI) for temperatures and CPU throttle rates and (c) low-level hardware sensors for motherboard temperatures and power supply voltages. By operating as a uniform software layer that sits above low-level health measurement tools, HAPI hides the idiosyncrasies of measurement and allows fault detection, prediction and recovery techniques to access data via standard mechanisms. HAPI supports both standard Linux clusters and the LANL Clustermatic toolkit.

To enable effective monitoring of systems containing thousands or tens of thousands of nodes, fault tolerance data collection must be scalable and integrated with low overhead performance measurement systems. We propose to develop statistical sampling schemes for this purpose. These sampling schemes will be adaptive, enabling configuration of sampling frequencies and sample sizes based on historical failure probabilities and user experiences.

#### Measuring Environmental Health and Impacts

Thermal stresses are also a major cause of component failures. An enterprise machine room contains a complex hierarchy of "micro-climates," ranging from within a single microprocessor, a motherboard and node, and a set of racks through raised floors, cooling ducts and ambient room temperatures. Often, physical configuration and placement can lead to unexpected and unknown (at least until failures occur) thermal stresses.

Building on the UNC HAPI infrastructure, we propose to develop a distributed measurement toolkit that exploits mobile environmental sensors that can be placed in machines, racks and air ducts. This toolkit will capture time varying temperature, humidity and vibration, enabling construction of machine room micro-climate maps and displays. This toolkit will be integrated with the health monitoring infrastructure and provide the raw data needed for constructing more accurate hardware failure models. In addition, it will enable more intelligent management of machine rooms by tracking the effects of hardware changes on the surrounding systems; often placement of new equipment can create thermal hotspots where none were expected.

#### **Analyzing and Modeling Performance and Reliability**

The data collected for a parallel application on an extreme-scale system can be overwhelming. Analysis and presentation techniques must support top-down analysis to cope with the complexity of programs containing millions of source lines running on thousands or tens of thousands of processors. To understand executions and reliability on such systems, it is not practical to inspect processors and tasks individually. Instead, improved analysis techniques are needed that can identify and correlate data from key subsets.

#### Analyzing Performance with Compile Time Information

Understanding the performance of programs with thousands of "moving parts" requires understanding the relationship of interactions between processes to the context in which these interactions occur. Resource contention (e.g. for access to I/O), serialization, and load imbalance are three problems that are difficult to understand. Serialization needs to be attributed to synchronization points. Resource utilization and contention must be attributed back to resource requests in context. Even understanding computation costs in modular programs can be difficult when multiple instantiations of code are present because of inlining and templates. In each case, the first step to understanding behavior is assessing the context in which it occurs. We propose to use calling context information collected with call stack unwinding as the basis for attributing costs to contexts. For programs with inlining or template instantiation, it is important to identify and attribute performance metrics correctly to inlined abstractions as well as the contexts into which they are inlined. To address this problem, we propose to extend capabilities in Rice HPCToolkit for binary analysis of executables to identify and accurately attribute performance for inlined code.

Comparing profiles based on different events, computing derived metrics (e.g., event ratios), and correlating profile data with routines, loops and statements in application code can provide application developers with insight into performance problems. However, on an extreme-scale system, an application developer cannot inspect data from every application or system component. To help users cope with the overwhelming volume of information about application behavior on extreme-scale systems, more sophisticated analysis strategies are needed for automatically identifying and isolating key phenomena of interest, distilling and presenting application performance data in ways that provide insight into

performance bottlenecks, and providing application developers with guidance about where and how their programs can be improved.

Better statistical techniques are needed for analyzing performance data and for understanding the causes and effects of differences among process performance. We have begun investigating bi-clustering techniques for identifying key differences between groups of processes. A second technique for coping with the number of components and the amount of performance data that can be collected on extreme-scale systems is to select a statistically valid subset of the components and model the members of that subset in detail. Properties of the subset can be used as a basis for estimates of the entire system. Our preliminary research in this area, so far, has explored using statistical techniques for analyzing system availability. The main objective of this research will be to evaluate how well application performance can be characterized and understood without exhaustive examination of performance data by developers.

An analysis challenge using message-centric monitoring is to account for indirect second-order performance effects without complete global information. Trace-based systems are able to find such indirect performance effects by paying the cost associated with keeping a global record of system activities across all nodes. Systems based purely on statistical monitoring cannot normally find such problems because there is no causal data and no cross-node data available. Unlike current statistical approaches, message-centric monitoring should be able to account for some of these effects because performance data follows the potential paths of indirect performance interaction.

The grand challenge for analysis of performance data to fuse data from processors, other hardware resources, software components, and communication into a form that provides insight into the full range of performance problems in parallel applications. A particular challenge is to achieve the insight possible with space-time diagrams from message traces without exhaustive tracing (which is expensive) or diagrams too large to be rendered.

# Modeling Application and System Performance and Reliability

The modeling of high performance software and hardware systems is highly complex and requires a deep understanding of the interplay of architecture and software at a variety of scales. The PAL team at LANL has focused on manual techniques for macroscopic modeling of parallel programs to gain insight into their expected performance on a range of parallel systems. A major thrust of modeling efforts so far at Rice has been to construct semi-automatically models of application performance at a fine-grain level to understand the interplay of the application's instructions with a microprocessor core and memory subsystem.

The resulting performance models can be used for analyzing node performance on both existing and proposed future architectures. In software development, these models can be used to pinpoint particular interactions between hardware and software features that are causing performance loss. Accurate models are a unique tool for architecture design. We propose to develop performance models of programs representative of ASC codes to understand their key performance characteristics and to understand how alternative architectures could improve application performance.

A focus of ongoing work is to assess the potential performance benefits and bottlenecks associated with emerging multi-core processors. Key issues of importance include understanding the impact of shared memory hierarchy components. Analysis of application models for multi-core processors should yield insight into what new compiler strategies will be needed to boost efficiency of multi-core chips. This problem may be complicated by active power management of multi-core chips – improving the compiler to generate tighter code for multi-core chips may ultimately hurt performance if this causes the core to be clocked slower because of high power dissipation.

#### Modeling Communication Performance

We intend to predict the performance of a parallel application as a function of its single node performance and its communication cost. This work will build on Rice's infrastructure for constructing models of single node performance. To understand the cost of communication, we must model the communication patterns of the application. We plan to extend our current binary analysis and instrumentation infrastructure to measure the volume of communication at each synchronization point. A synchronization point is defined by a call to a communication function. The user can specify the set of communication functions to be monitored at instrumentation time.

For each process of a parallel application, we propose to collect a trace of synchronization events interleaved with the histogram of basic blocks that were executed in each synchronization interval. At each synchronization point, we will collect the size of messages exchanged with each communication partner. We will aggregate the collected data per computation interval, where a computation interval is uniquely determined by the addresses of the call instructions at its two endpoints.

For each such interval, we will know the communication functions invoked at its starting point and its ending point, the number of times the interval executed, the distribution of message sizes sent and received at its starting point (stored as a histogram), and the histogram of basic blocks and edges executed during the interval.

For each synchronization interval we plan to model the distribution and structure of the histogram of message sizes exchanged at its starting point as a function of node problem size, or/and as a function of the number of processes. This problem is similar to modeling the distribution of memory reuse distances seen by a memory reference, and we plan to use a similar modeling approach. Like reuse distance, communication volume is a machine independent application characteristic. Thus, the models of communication patterns constructed in this fashion are portable across architectures, and for predictable applications, we expect the models of communication histograms will be highly accurate.

To compute computation cost between synchronization points, we will need to modify our instruction scheduler to reconstruct executed paths in partial control flow graphs. To determine the overlap between communication and computation, the user must specify for each communication function if it is synchronous or asynchronous. For synchronous synchronization points, there is no overlap between communication and computation, and the execution cost of an interval is the sum of its aggregated communication cost and its aggregated computation cost.

For asynchronous synchronization points, a simple model for the execution time is to consider the maximum between the communication and computation costs, plus an eventual communication start-up cost. However, such a model is likely to under-predict the execution time because for each synchronization interval we have a distribution of exchanged message sizes, and an aggregation of basic blocks executed during all traversals of current interval. This information is not enough to match the communication cost and computation cost of each traversal. It may happen that for some executions of the interval the cost of communication is larger than the computation cost, while for other executions the computation cost is higher. In such a scenario neither aggregate cost is completely hidden. Understanding the level of overlap for arbitrary programs is a difficult problem and will require further study.

#### Modeling Failure and Integrated Performance/Failure

During the past year, the UNC team has implemented a framework where failure and performability models can be implemented and evaluated. The Failure Indicator Toolkit (FIT) is a library that supports gathering of health-related diagnostic information, developing statistical models of normal system health, and determining the probability that recent health information indicates a failure mode. FIT collects health data via the HAPI library, and it can also be stored for offline analysis and experimentation.

FIT currently features a single failure predictor that makes a binary failure/no failure prediction based on a threshold applied to a single health information datum. We propose to implement sophisticated statistical models for health classification including hidden Markov models, neural networks, and Bayesian probability approaches. Each model will be automatically trained on known good health data. Once the model is trained, failure prediction takes place whenever new health data is available.

The FIT framework makes comparing the predictive accuracy of different models on the same health data an easy task, allowing for quick determination of which model(s) work best with the data. As part of this work, we will develop rules-of-thumb for matching health information sources to appropriate failure predictors. Finally, we will develop and expand performability models that combine both fault-tolerance and performance for systems containing thousands of nodes. These models will include total time to solution as a function of failure modes and probabilities.

#### **Improving Performance and Reliability**

Raw performance and reliability data are the inputs to analysis tools. From manual, semi-automatic and automatic analysis come insights into the causes of poor performance or reliability and opportunities to address these problems. Our goal is to develop tools and approaches that can help applications achieve high performance even when system components fail or applications are subject to other system constraints. Strategies for automatic performance steering based on performance and fault models offer the potential to enable long-running programs to repeatedly adjust themselves to changes in the execution environment – perhaps to opportunistically acquire more resources as they become available, to rebalance load or adapt to component failures. Moreover, measurement of environmental conditions on nodes promises to allow users and schedulers to balance checkpoint frequency and partition allocation based on failure likelihood.

In addition, validated performance "contracts" among applications, systems, and users that combine temporal and behavioral reasoning from performance predictions, previous executions, and compile-time analyses are one promising approach. This work will explore using performance contracts to guide the monitoring of application and resource behavior; contracts will include dynamic performance signatures and techniques for locally (per process) and globally (per application and per system) evaluating observed behavior relative to that expected.

#### Improving Reliability through Fault Tolerant Algorithms

Coping with the failure of system and application components is difficult. We propose to create a framework, which we call FT-LAP, that will simplify the development and implementation of fault tolerant software libraries by providing support for detection process faults, and recovery of data in the presence of multiple process failures and high failure rates. The FT-LAP framework will

- exploit *diskless checkpointing*, which offers unique advantages for resiliency and performance in the massively parallel environments that we are targeting,

- build on fault tolerant MPI (FT-MPI)—a state of the art implementation of the MPI standard constructed by a team led by Dongarra that has extended failure semantics and corresponding mechanisms to enable applications to detect and recover from faults at levels of functionality previously unattainable, and

- take an *algorithm-centered approach* to fault tolerance that maximizes programmer opportunities to utilize application specific knowledge to achieve the kind of unprecedented efficiency and performance that future high end computing environments will demand.

To survive multiple process failures by using as small processor redundancy as possible, we propose to use error-correcting techniques to encode the local checkpoint data and store the encoded data into some dedicated checkpoint processes.

Diskless checkpointing requires that each process maintain a local copy of the checkpoint data in the local memory of each process, so that a consistent state can be reconstructed during recovery. Diskless checkpointing approach is especially appropriate for iterative methods. In most iterative methods, the application will synchronize on each iteration and modify only a small amount of its state between iterations. This implies that only a very small amount of data needs to be checkpointed and hence a very low fault tolerance overhead is possible. If a smaller amount of extra memory is available in each process, then we propose to use a reverse computation-based technique combined with error correction coding.

To enable a seamless computing environment offering interchangeability of compute resources and scalability from the desktop to thousands of (heterogeneous) processors including coarse grained multiprocessor supercomputers, we will develop a framework for the development and implementation of fault tolerant software libraries for the core linear algebra area that will enable easy diskless checkpoint, detection process faults, and recovery of data in the presence of multiply process failures We propose to incorporate into libraries the techniques runtime support for adaptive strategies to allow diskless checkpointing during the course of execution, produce a design for extensions to provide recovery and process initiation in the presents of faults, exploit both loss-less and lossy approaches in recovery from faults in the execution of the libraries, and produce a set of "recovery libraries" for use in application studies, and evaluate their use in practical settings.

#### Improving Application Reliability via Adaptivity and Recovery

To support applications on large-scale systems, more active techniques are needed that enable systems and applications to continue operating even when some components fail. Without such schemes, the mean time to failure (MTBF) of systems with tens of thousands of commodity components, even when operated as quasi-independent partitions, will continue to decline and will severely limit solution feasibility for complex problems.

As noted earlier, health monitoring and failure prediction tools alone enable post-mortem analysis of failures. To increase the MTBF for applications and systems, online techniques are also needed that enable developers and applications to adapt program behavior. The use of tens of thousands of commodity components to increase peak performance will lead to intolerable failure rates without appropriate power management. Monitoring and analysis of power-performance profiles of scientific applications will be needed to optimize power consumption while maintaining performance. This will be particularly true for systems with multi-core chips.

A second way health monitoring information can be used is to improve reliability is to let an application use it to choose hardware partitions and checkpoint frequencies based on the application's own resilience to failures and models of anticipated failures. We propose to develop batch queue selection mechanisms that will allow application developers to select batch queues based on likely failure probabilities and modes. Intuitively, applications that are more resilient to transient errors (e.g., memory word or message bit upsets) due to internal consistency checks or varying memory footprints are more likely to complete successfully on less reliable hardware.

We will also develop an adaptive toolkit for application checkpointing that will choose checkpoint frequencies automatically as multiples of a user-specified threshold. For example, if an application could potentially checkpoint its state every K iterations, the adaptive toolkit would trigger a checkpoint every cK iterations, where c is determined based on acceptable overhead and probability of failure.

#### **Evaluating the Promise of Architectural Alternatives**

As architectural complexity rises, with multicore chips, network interface processors, complex storage hierarchies (memory and I/O), and the rise of special purpose co-processors, understanding the relative performance and reliability advantages that accrue from these alternatives is increasingly critical. We propose to develop a suite of tools that can be used to assess these tradeoffs.

In particular, Los Alamos and other laboratories are evaluating alternate architectures that exploit FPGAs and graphics processors (GPUs) for high-speed computing. These systems combine FPGAs or GPUs with standard nodes, offloading computation intensive routines to the auxiliary processor. With this additional complexity comes additional failure modes, power and temperature management (GPUs are notoriously hot) and options regarding data reuse and computation overlap.

We propose to explore the monitoring, adaptation and reliability issues associated with these hybrid systems, using the tools and techniques outlined in this statement of work. In particular, we plan to use data gathered using message-centric monitoring to analyze application performance and to analyze architectural issues to understand performance tradeoffs among improvements in network bandwidth, computing power, and storage performance.

In addition, by understanding the interplay of instructions in an application's core loops, understanding the temporal and spatial locality (or lack thereof) of memory reference patterns, one can assess whether an application can be more effectively performed with an FPGA, a GPU, a processor-in-memory or a vector unit rather than a microprocessor core. Our aim is to provide semi-automatic tools for assessing alternatives for arbitrary applications by combining static and dynamic information into detailed loop-level models of application performance.

#### 1.1.3 Project Tasks

#### FY06:

- Develop and deploy techniques and tools for call-stack sampling based monitoring and analysis

of parallel codes.

- Design and implement software interfaces for using off-processor counters to assess application performance and reliability.

- Develop and validate stratified sampling for scalable monitoring of performance and system health.

- Evaluate message-centric monitoring of LANL-relevant applications on large-scale systems.

- Use message-centric monitoring to drive load-balancing decisions on dynamic applications.

- Integrate tools for vertical and horizontal message-centric monitoring.

- Evaluate statistical methods for analyzing performance data from extreme-scale systems.

- Develop basic "micro-climate" sensor infrastructure for rack and machine room monitoring.

- Assess prototype failure indicator and prediction mechanisms for predicting likely component failures.

- Develop adaptive checkpoint schemes based on failure indicators.

- Assess and couple prototype batch queue selection mechanisms with failure indicator toolkit.

- Design and prototype diskless checkpointing in which the checkpoint processes participate in the computation and rearrange data when a failure occurs. Use *p* processors for the computation and have *k* of them hold checkpoint.

- Evaluate algorithms for coordinating local checkpoint/restart in which processors hold backups of neighbors.

- Evaluate processor/co-processor system performance based on FPGAs and GPUs.

#### FY07:

- Develop a prototype that semi-automatically produces models of communication performance for parallel applications using a combination of static and dynamic analysis.

- Extend and apply micro-climate senor infrastructure and integrate with health/performance monitoring toolkits.

- Adaptively tune online message-centric monitoring to balance accuracy and overhead.

- Use online monitoring information for detecting operating system-caused performance anomalies.

- Design, and prototype integrated analysis capabilities that provide a global view of application performance by combining information from communication analysis with node-level performance data.

- Develop software to determine the checkpointing interval and number of checkpoint processors from the machine characteristics using historical information. Migrate tasks if a potential problem is noticed.

- Coordinate and couple integrated health/performance monitoring and failure prediction with checkpointing, back queue selection and adaptation policies.

- Develop and extend processor/co-processor adaptability (i.e., the ability to trigger execution of adaptive libraries on processors or co-processors based on expected performance gains).

#### FY08:

- Design and prototype measurement and analysis tools for emerging architectures. Focus: forthcoming HPCS architectures.

- Expanded evaluation of integrated adaptation and performance/reliability schemes with target applications.

- Evaluate processor/co-processor infrastructure with target applications.

- Evaluate checkpointing with "real applications" and investigate "lossy" algorithms.

- Generalize the prior prototypes to provide a library of routines to do the diskless checkpointing.

#### 1.1.4 Relevance to Weapons Program

The findings from this research, as well as tools and software infrastructure developed as products of this effort, are expected to benefit all ASC application teams. The aim of this research is to provide ASC application teams with

- better methodology and tools for measuring application performance, resource utilization, and system health,

- better techniques and tools for analyzing program and system performance and reliability,

- insights into the interplay between applications and systems that leads to better mapping of applications onto current and emerging extreme-scale systems,

- strategies and mechanisms to support construction of failure-resilient programs, and

- insights into the nature of extreme-scale parallel architectures and applications that will help improve the design of future systems.

Better tools and techniques to monitor and analyze application performance on current-generation architectures are a good investment for both the short and long term. In the short term, they help pinpoint bottlenecks in existing applications; this enables scientists tune applications for better performance. Over the long term, understanding performance bottlenecks and reliability limitations in today's applications and systems will focus research on practical software and hardware technologies that hold the most promise for improving performance and scalability of future applications on the next generation of computer systems.

### 1.2 Compiler Technology for High-Performance Computing

#### Supported Personnel:

**Project Leads:** John Mellor-Crummey, Rice, johnmc@cs.rice.edu; Ken Kennedy, Rice, ken@cs.rice.edu, Keith Cooper, Rice, keith@cs.rice.edu

Other Supported Personnel: Rice: Tim Harvey, Guohua Jin, Robert Fowler

LANL Point of Contact: Rod Oldehoeft, rro@lanl.gov

#### 1.2.1 Vision

Programming extreme-scale systems efficiently is very difficult. Difficulties exist at two levels: writing parallel programs and generating efficient code for processing elements.

Writing parallel programs is hard because parallel programming models today require users to manage resources of parallel systems at a very detailed level. When using MPI – the dominant programming model for writing scalable parallel programs – programmers must partition application data structures and computation, add data movement and synchronization, and manage storage for non-local data. Because of the explicit nature of MPI communication, significant compiler optimization of communication is impractical. For this reason, all responsibility for optimizing communication performance falls to application developers. For high efficiency, application developers must choreograph asynchronous communication and overlap it with computation. This complicates parallel programming significantly.

Higher-level programming models that simplify the construction of parallel programs are needed. However, for high-level programming models to succeed, they must meet a number of requirements. First, they must be ubiquitous; otherwise they will be unattractive to application developers. In practice, this means that in addition to being available on extreme-scale systems, they must also execute on laptops and clusters. Second, high-level programming models must be expressive and conveniently support a wide range of algorithms and programming techniques. Ideally, high-level programs should be easy to write, read, maintain, and reuse. Third, the efficiency of code generated from high-level programs must be comparable to that of the best hand-coded low-level parallel programs. Finally, to attract application developers, high-level models must have a promise of future availability and longevity.

Regardless of how programs are written for extreme-scale systems, solving large-scale problems requires using processor nodes as efficiently as possible. Failure to do so would increase the time to solve problems on processor ensembles of a fixed size or require larger systems to maintain the same time to solution. The effects of efficiency gains made at the level of individual nodes are multiplicative. For this reason, compiler technology for generating efficient code for processor nodes is of critical importance.

#### 1.2.2 Compiler Technology for Parallel Systems

Today, fragmented programming models such as MPI require application developers to explicitly manage separate address spaces for each processor as well as manage communication and data movement. Highlevel programming models that abstract away the details of how computation is partitioned as well as data movement and synchronization are needed if we want to increase the productivity of application developers.

Whether programming for single chip multiprocessors such as Cell, or large-scale parallel systems, one should be able to use a simple programming model and compilers should take care of the details of managing data movement and synchronization without sacrificing much of the performance that could be achieved by hand coding. Global address space programming models offer the simplest abstraction for expressing parallel programs. We believe that global address space programming models are the appropriate model for programming a wide range of parallel systems from single-chip multiprocessors to emerging large-scale parallel systems such as Cray's Red Storm and systems that we expect to arise out of DARPA's HPCS project.

SPMD global address space programming models such as Co-array Fortran (CAF) and Unified Parallel C (UPC) offer promising near-term alternatives to MPI. Programming in these languages is simpler: one simply reads and writes shared variables. With communication and synchronization as part of the language, these languages are more amenable to compiler-directed communication optimization. This offers the potential for having compilers assist effectively in the development of high performance programs. Research into compiler optimizations for SPMD programming languages offers the potential of not only simplifying parallel programming, but also yielding superior performance because compilers are suited for performing pervasive optimizations that application programmers would not consider employing manually because of their complexity. Also, because CAF and UPC are based on a shared-memory programming paradigm, they naturally lead to implementations that avoid copies where possible; this is important on modern computer systems because copies are costly. We propose to explore the utility of SPMD global address space programming models for parallel programs of interest to the LANL.

Beyond explicitly parallel SPMD programming models, data-parallel models such as High Performance Fortran and Cray's Chapel language offer an even simpler programming paradigm, but require more sophisticated compilation techniques to yield high performance. Research into compiler technology to increase the performance and scalability of data-parallel programming languages as well as broaden their applicability is important if parallel programs are to be significantly simpler to write in the future. For parallel programming models to succeed, their use and appeal must extend beyond just extreme-scale machines; therefore, sophisticated compiler technology is needed for these languages to make them perform well on today's relatively loosely-coupled clusters as well as tightly-coupled petascale platforms of the future. We propose to investigate compiler technology that makes it possible to execute high-level data parallel programs efficiently on systems ranging from single-chip multiprocessors such as Cell to commodity clusters.

#### 1.2.3 Compiler Technology for Node Programs

Achieving high levels of performance on modern computer architectures requires careful planning and execution at every level of the tool chain that translates the application's source text into executable code for the target machine. Various tools must identify large-grain parallelism and use it to occupy multiple processors. They must design appropriate strategies to pass data between the distinct threads of the computation, insert the code to implement the needed communication, and adjust the strategy to balance communication and computation. The tools must ensure that the code, as translated, has a memory reference pattern that takes appropriate advantage of the multiple levels of memory hierarchy, blocking for one or more levels of cache and for register reuse. The final steps of translation map this carefully planned behavior into the instruction set of the target machine and try to balance the needs of the computation against the processors' actual resources. To achieve high performance, all of these steps must be done well.

At this final level of translation, backend optimization and code generation algorithms strongly influence the final performance of an application. The major concerns at this level of translation include: 1) keeping the functional units busy, 2) hiding the latencies inherent in the processor and memory system, and 3) ensuring that the final code uses the processor effectively. The current generation of open-source compilers (and their commercial cousins) routinely produces code that obtains 5 to 10% of the processor's peak performance. In part, this underperformance arises from the use of backend optimization and code generation algorithms that were developed for systems with much simpler performance characteristics.

In this project, we will examine several specific backend compiler problems that appear to have an impact on the performance of ASC applications. In particular:

- Changing the instruction mix: In the instruction stream of a running application, the mix of operations that the processor encounters should match the set of functional units that the processor provides. A mismatch between application operations and processor capabilities leads to saturation for one set of functional units and starvation for another. We have begun an investigation into automatic techniques that use backend optimization to alter an application's instruction mix. Our initial work has focused on critical loops of Sweep3d. This example suggests that the problem will require a coordinated attack by a small suite of backend optimizations.

- Aggressive rematerialization: The high costs associated with accessing memory present a significant performance challenge on modern systems—one that will continue to grow as memory latencies increase and as the number of CPU cores per chip increase. Techniques that can reduce the number and frequency of memory accesses should improve application performance. Rematerialization is a code generation strategy that recomputes certain values when doing so is less expensive than accessing them from memory. Today, it is applied in register allocators to values that can be computed in a single operation and whose operands are all available a standard that misses many profitable opportunities. We will develop a standalone rematerialization algorithm (outside the allocator) that uses a tunable metric to determine profitability. The resulting technique should directly reduce memory accesses and indirectly reduce cache disturbance from scalar loads.

- Scheduling and register allocation: A major open challenge in code-generation algorithms lies in coordinating the behavior of instruction scheduling and register allocation. Prior work in this area has produced algorithms that coordinate their behavior but favor one process over the other—either underallocating registers to reduce constraints on the scheduler or limiting the scheduler's ability to move operations when such motion increases demand for registers. Early work by Schielke shows the potential for a truly fair technique to find improvements in both scheduling and allocation—reducing stalls and spills at the same time. Unfortunately, his technique relied on extensive randomization and hundreds of trials, making it impractical for routine use. We will explore algorithms that solve these problems together, working in the context of the Callahan-Koblenz register allocator that we have built for LLVM.

All of these explorations will be conducted in the code context of one of the two open-source compiler systems, Open64 or LLVM, that we believe are viable candidates for future development. We will work with external collaborators on LLVM and Open64 to help ensure that there are viable open source compilers for directly transferring compiler research to the ASC program. In each investigation, we expect to apply the lessons that we have learned in designing adaptive techniques as part of the LACSI Autotuning effort. We will test the algorithms on ASC-related codes.

# 1.2.4 Proposed Milestones

#### FY06:

- Report intermediate results of ongoing work on techniques to change the instruction mix in performance critical loops. (Quarter 1)

- Perform experiments with additional codes for instruction-mix modification (Quarters 2—4) and develop a strategy to deliver this technology. (Quarter 4)

- Develop an initial aggressive scheduler for LLVM. (Quarters 1 and 2)

- Refine parallel compiler analysis and code generation techniques for dense matrix codes to efficiently support programs with strided alignments, such as multigrid.

#### FY07:

- Design and prototype data-parallel compiler technology to map application codes to single-chip multiprocessors with explicitly-managed memory (such as Cell).

- Design and implement a tunable rematerialization pass for LLVM (Quarter 2), followed by experimental evaluation and report (Quarter 4)

- Initial version of algorithm for combined scheduling and allocation (Quarter 2)

- Design and implement prototype compiler and run time support for general block distributions.

- Design and implement a prototype compiler that uses data-parallel compiler technology to map application codes to ensembles of single-chip multiprocessors with explicitly-managed memory (such as Cell).

#### FY08:

- Refine a combined scheduler and allocator (Quarters 1 and 2); distribute as part of the LLVM compiler (Quarter 4)

- Distribute aggressive rematerialization pass for LLVM (Quarter 2)

- Develop prototype compiler and run time support for user-defined block distributions in high-level models for parallel programming.

### 1.2.5 Relevance to Weapons Program

One aim of this research is to produce efficient high-level programming models suitable for future ASC applications. A second aim of this research is to develop compiler technology that will make it possible to use compute nodes in extreme-scale systems efficiently. The findings from this research and software infrastructure, developed as products of this effort, are expected to benefit all ASC application teams.

# 2. Components

# 2.1 Component Architectures for High Performance Computing

#### Supported Personnel:

**Subproject Leads**: Ken Kennedy, Rice, <u>ken@cs.rice.edu</u>; Jack Dongarra, UTK, dongarra@cs.utk.edu

**Other Supported Personnel:** *Rice*: Zoran Budimlic, Rob Fowler, Guohua Jin, Cheryl McCosh, John Mellor-Crummey

LANL Point of Contact: Craig Rasmussen, <a href="mailto:rasmussn@lanl.gov">rasmussn@lanl.gov</a>

#### 2.1.1 Vision

The goal of component architectures research is to make it easy to develop high-performance applications by using compiler-based tools to integrate components from pre-existing libraries. By providing modularity through well-defined component interfaces, component integration systems permit scientists and software developers to focus on their individual areas of expertise: scientists can concentrate on integrating applications by gluing domain-specific components together using some form of scripting language, leaving the development of those components to expert programmers. In addition, because components foster more code reuse, they provide an increased economy of scale, making it possible for resources to be shifted to areas such as performance engineering, testing, and platform adaptation; the result is improved software quality, portability, and application performance.

A fundamental obstacle to this strategy is that scientific application developers, particularly those at Los Alamos National Laboratory, cannot afford to sacrifice significant amounts of performance for this clearly useful functionality. An important objective is to produce applications without sacrificing performance relative to hand-integrated codes. To address this problem, the component integration research effort is exploring integration strategies that perform context-dependent optimizations automatically as a part of the integration process. This theme defines a significant portion of the research content of the work described in the remainder of this section.

In the strategy we envision, applications would be defined using high-level scripting languages such as Matlab or Python to coordinate invocation of library operations, although traditional languages such as Fortran and C++ could also serve this purpose. Because scripting languages typically treat library operations as black boxes that cannot be optimized to the contexts in which their invocations appear, these systems often fail to achieve acceptable performance levels for compute-intensive applications. One solution strategy that has been successfully employed in previous research is to translate scripts to a conventional programming language and use whole-program analysis and optimization to improve performance to acceptable levels. The main drawbacks of this approach are long script compilation times and the absence of an effective way to exploit the domain knowledge of library developers.

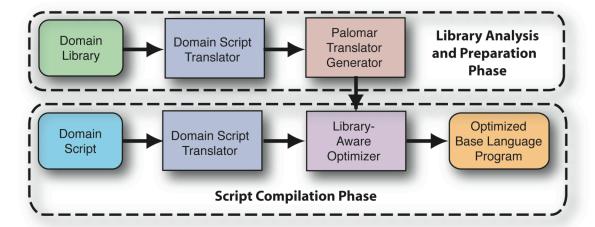

To address these problems, this project is pursuing a new approach called "telescoping languages," in which libraries that provide component operations accessible from scripts are extensively analyzed and optimized in advance. In this scheme, depicted in the figure below, language implementation consists of two phases. The offline *library analysis and preparation phase* digests annotations describing the semantics of library routines, combines them with its own analysis to generate specialized variants of each component in the library. In addition, it produces a *library-aware optimizer* that understands library entry points as language primitives. The *script compilation phase* can then use the generated compiler to produce an optimized base language program.

We will use this strategy to attack the problem of making component integration efficient enough to be practical for high-performance scientific codes. Of particular importance in this context is the problem of efficiently integrating data structure components (e.g., sparse matrices) with functional components (e.g., linear algebra). We will also explore the use of high-level prototyping languages, such as Matlab and Python, as the scripting languages for application definition.

If this effort is to succeed, it must take into account an important reality: many components will be constructed using object-oriented languages, so techniques for optimizing such languages are critical. We plan to invest a significant effort in analysis and optimization of components written in C++, Java, and Python.

# 2.1.2 Research Plan

To achieve the project vision, we plan to conduct research that focuses on *supporting technologies for component integration*, which include:

- Transformation systems to eliminate overheads due to abstraction. These systems will employ

high-level context information to select the right variants of components for a given calling

context and employ macro-transformations that replace expensive sequences of component

invocation with more efficient sequences in the given context.

- Component integration systems that automate specialization. We will also explore component

integration frameworks that generate specialized versions of certain components for common

calling context and substitute those specialized versions, statically or dynamically, in applications

that employ those components.

A driving problem for this research is to construct component integration frameworks that can efficiently integrate data structure components with functional components. An example would be the integration of sparse versus dense array data structures with certain types of linear algebra operations. This has been an important goal of the generic programming research area, and success will require advances in both component design and transformation-based integration frameworks.

In this work we will continue our efforts to collaborate with weapons code projects at LANL. Of particular importance is the collaboration with the Marmot Project, because that project is attempting to apply modern software design and integration strategies to code development. We will continue to execute the draft collaboration plan (described below) that was developed in workshops with the Marmot team. In addition, we will develop new collaborations with the traditional code teams.

As a driving problem, our work will focus on an unclassified, export-restricted test code that is representative of LANL codes that combine hydrodynamics with radiation transport. We will also explore important related codes from the Telluride and Marmot projects.

With these considerations in mind, we plan to pursue research in four fundamental directions:

Advanced Component Integration Systems: This effort will explore the application of telescoping languages technology to the component integration problem, with a particular emphasis on integrating components that support data structures with those that implement functionality. The effort will also consider technologies for optimizing accesses to the component interfaces emerging from LANL weapons-related code development efforts. The long-term goal of this research is to produce a component integration framework that is efficient enough to be accepted by high-performance application developers, such as those in the LANL ASC program.

Some specific research challenges in this area include:

Exploration of array and mesh abstraction. We will investigate the issue of separating content and layout in an array abstraction. The specific issue is whether it is possible to easily substitute different data layouts for the same abstract data structure without substantively changing the functional components that use them. This research touches on the extensive research in "generic programming" because it may require some coding standards for functional components to achieve maximum flexibility. However, all data-layout-specific code will be encapsulated with the data structure component.

Preliminary work on this effort will be conducted in the context of Matlab (or Python), beginning with the definition of a generalized array data structure that incorporates data distribution. Specific array distributions for sparse matrices will be explored as a way of understanding the crucial performance issues. (This may contribute to work on a parallel version of Matlab, described below.) Once the Matlab array prototype has been explored, we will focus on ASC mesh data structures with the goal of demonstrating a prototype with adequate efficiency for use in production codes based on these components. The ultimate goal is to make it possible to quickly substitute different mesh data structures in a code without rewriting the functional components and vice versa.

The development of new specialization strategies for components. As a specific challenge, we will explore static and dynamic approaches to reduce the time and space required to deal with specialization of multiple materials in cells. This problem arises because many codes iterate over all potential materials that might occur in a cell, even though most cells will have far fewer than the maximum number of materials. If pre-specialized code can be generated for the cells with small numbers of materials, it may be possible for the right specialized variant to be selected statically or dynamically, saving substantial space and time. The goal is to permit the developer to specify the handling of materials in the most general way possible, and let the compiler and run-time system handle the specialization. These strategies can be further enhanced by compiler-based specialization to sparse data structures and by reorganization of computation to deal with block of cells with similar properties at the same time.

Demonstration of these techniques in specific applications of interest to ASC and LANL. We will continue to seek appropriate applications within the weapons program. To that end, we will use Sage and Sweep3D to represent a standard hydrodynamics and radiation transport application. We will also continue to work with the Marmot and Telluride projects to find representative applications that can be analyzed at the participating universities under export restrictions.

Construction of Efficient Specialized Libraries for Component Integration: This effort will focus on the generation of component libraries that can be incorporated into high-performance applications and can be the bases for domain specific problem-solving environments. Significant issues will be flexibility and adaptability of the components to both the computations in which they are incorporated and the platforms on which they will be executed. The effort will also focus design strategies for efficient data structure components.

Under this project we plan to pursue the following specific research directions

- Tools for Pre-optimization of Libraries: We will explore some component libraries that are used within the weapons program to identify opportunities to pre-specialize them to expected calling context. One early target for this work will be Trillinos.

- *Mining of Traditional Applications:* We will explore automatic strategies for mining traditional applications and libraries to construct component libraries that might be employed in other applications. In particular, we are interested in exploring the automated translation of older applications into script-based domain languages, in which components of the original program form the library underlying the domain language.

- Annotation of component libraries for efficient integration via a telescoping languages framework: This effort will develop annotation strategies, along with the associated transformation systems, that will make it easier to optimize component accesses within applications and to replace sequences of calls to library components by more efficient sequences.

- Factoring of Components for Efficient Recombination: This work will involve research into the proper structure of libraries so that efficient variants can be synthesized from component pieces once the calling context and target platform is understood.

Compilation and Optimization of Object-Oriented Languages: Object-oriented languages like C++, Java, and Python have a number of attractive features for the development of rapid prototyping tools, including full support for software objects, parallel and networking operations, relative language simplicity, type-safety, portability, and a robust commercial marketplace presence leading to a wealth of programmer productivity tools. However, these languages have significant performance problems when used for production applications. In this effort, we are studying strategies for the elimination of impediments to performance in object-oriented systems.

To achieve this goal, we must develop new compilation strategies for object-oriented languages such as C++, Java, and Python. This should include interprocedural techniques such as inlining driven by global type analysis and analysis of multithreaded applications. This work would also include new programming support tools for high-performance environments. Initially, this work has focused on Java, through the use of the JaMake high-level Java transformation system developed at Rice in collaboration with the LANL CartaBlanca project. This system includes two novel whole-program optimizations, "class specialization" and "object inlining," which can improve the performance of high-level, object-oriented, scientific Java programs by up to two orders of magnitude.

In the next phase of research, we will consider how to adapt these strategies to develop tools and compilation strategies that would directly support the code development methodologies to be used in the Marmot effort. Examples include not only the application of object inlining and class specialization, but also the use of type analysis to support the elimination of dynamic dispatch of methods, a major problem for high-performance codes written in C++. We will also consider ways to apply these compilation strategies to Python used as a high-level application prototyping system.

**Rapid Prototyping in High-Level Scripting Languages:** In this effort we will explore the use of scripting and problem-solving languages such as Matlab and Python for the development of high-performance applications. A major problem is how to implement such languages on parallel machines. We plan to pursue two interrelated strategies in this effort. The first will explore a client server architecture in which the server is a parallel cluster and the client is a desktop computer. The second is a compiler-based strategy. These are described in more detail in the following paragraphs.

Matlab optimization via cluster-based computation. We focus our attention on how to provide parallel computation capabilities to such environments that would allow for seamless access to hardware and software resources for numerical linear algebra. Instead of focusing on a particular implementation, we are exploring the design space of such an interactive environment such as Matlab, Python, and

Mathematica and the consequences of particular design choices. We have developed a prototype implementation of our ideas with emphasis on the performance perceived by the end user. In our design, we consider primarily a client-server architecture where the server is envisaged as a cluster and the client is a simple desktop computer.

At the moment, the basic infrastructure of our design has been implemented and successfully applied to a dense matrix factorization and iterative solution method in Matlab and Python environments. Our preliminary tests show that the overhead of remote execution can be offset when problem sizes become prohibitive for a sequential environment and it is possible to reap the benefits of parallel computation.